Für Produktanfragen kontaktieren Sie uns über

- das Kontaktformular,

- E-Mail (sales@suragus.com) oder

- Telefon (0351 32 111 520).

Nachdem die International Technology Roadmap for Semiconductors (ITRS) in den Ruhestand geht und die International Roadmap for Devices and Systems (IRDS) die Aufgabe übernommen hat, einen Fahrplan für die gegenwärtigen und zukünftigen Technologien für die nächsten 15 Jahre zu erstellen, liegt der Schwerpunkt auf einem Blick, der weit über CMOS hinausgeht. Die Einführung der Hetergenous Integration Roadmap (HIR) unterstreicht die Notwendigkeit, Systeme zu bauen, d.h. die Integration von unabhängig voneinander hergestellten Komponenten in hochentwickelte Module und Gehäuse. Es wird erwartet, dass diese Baugruppen deutlich verbesserte Funktionalitäten und Betriebsleistungen aufweisen. Mit SiP, 3D- und 2D-Verbindungen und Wafer Level Packaging (WLP), die als drei wichtige Technologiebereiche für die heterogene Integration identifiziert wurden, entwickelt sich das Advanced Packaging in der Halbleiterfertigung rasch weiter, indem es sich mit den wichtigsten Faktoren auseinandersetzt:

Es wird erwartet, dass die 4 führenden Advanced-Packaging Formfaktoren – Fan-out Wafer-Level Packaging, SoIC/ Chiplets, 3D-TSV/ Interposer, doppelseitige SIPs – hochwertige Lösungen für die wachsenden Märkte bieten werden:

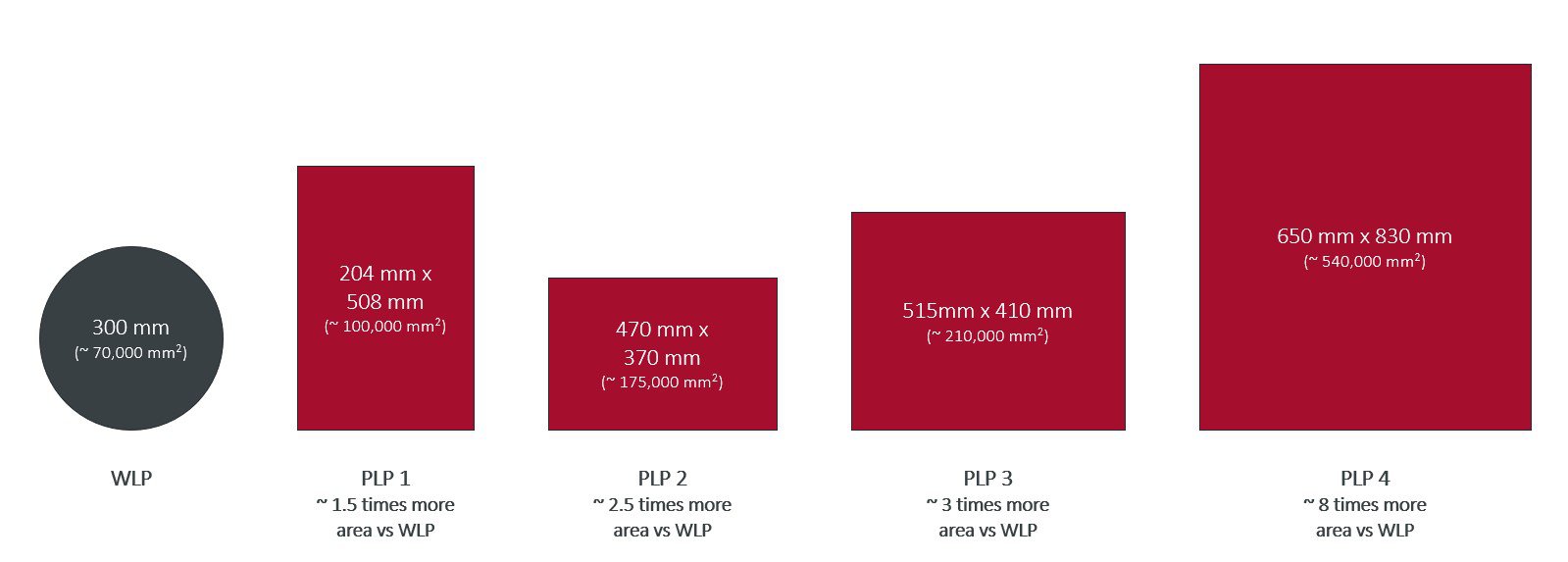

Neben der technologischen Entwicklung hin zur heterogenen Integration werden auch größere Substratformate in Betracht gezogen. Die derzeitigen Fertigungsmöglichkeiten auf Waferebene reichen bis zu 12"/300 mm. Um eine höhere Produktivität und niedrigere Kosten zu erreichen, werden größere Formfaktoren angestrebt. Obwohl 450 mm der Fahrplan auf Waferebene ist, könnte er umgangen werden, um sich dem Panel Level Packaging (PLP) zu nähern, was der nächste große Schritt sein könnte. Mit ihrem immensen Potenzial zur Miniaturisierung und heterogenen Integration bieten beide Technologieansätze viele Möglichkeiten und Vorteile für den Aufbau hochleistungsfähiger Systeme. Es wird erwartet, dass die PLP-Route den etablierten Standards in der LCD- und PCB-Fertigung folgt und damit die Entwicklungs- und Kommerzialisierungsziele beschleunigt.

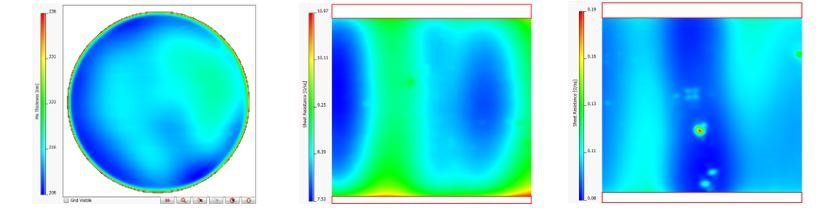

Je größer die PLP-Fläche ist, desto mehr Chips werden produziert und desto mehr Geräte und Systeme können hergestellt werden. Die großflächige Metallabscheidung durch PVD- und ECD-Technologien im WLP- und PLP-Verfahren eröffnet neue Wege zur Inline- oder Offline-Charakterisierung von Dünnschichten, insbesondere durch berührungslose und zerstörungsfreie Methoden. Für die hohen Durchsatzanforderungen charakterisiert die Hochfrequenz-Wirbelstromtechnik den Schichtwiderstand, die Leitfähigkeit, die Dicke und die Homogenität von Metallschichten.

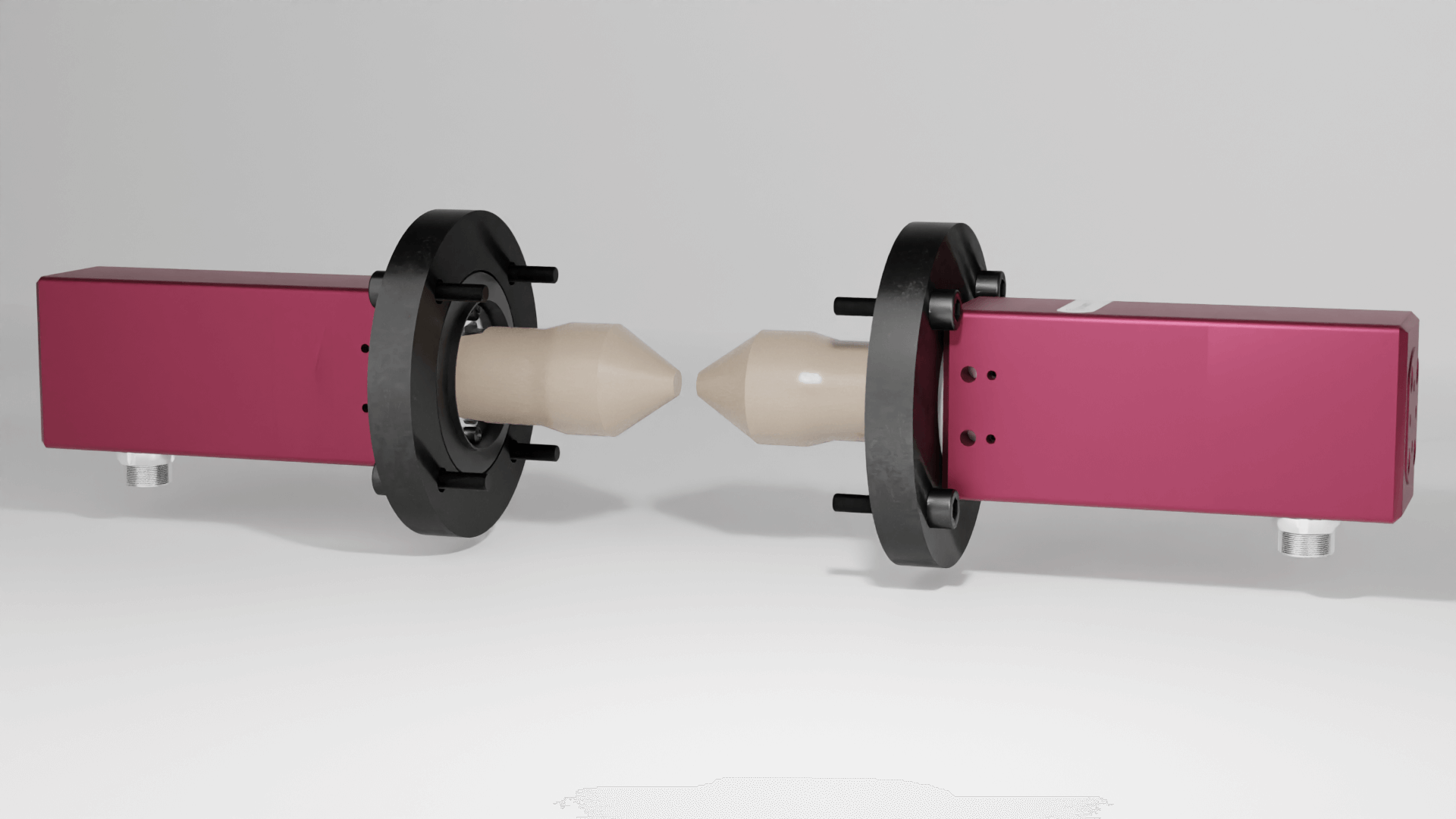

Durch das Packaging von integrierten Schaltkreisen direkt auf dem Wafer oder Panel kann ein Teil der erforderlichen Prozessschritte minimiert werden um so den Anforderungen in der Halbleiterindustrie nach Miniaturisierung bei gleichzeitig hohem Kostendruck nachzukommen. Die Hochfrequenz-Wirbelstromtechnologie ist ein geeignetes Verfahren für die Charakterisierung von Wafer und Panel bei hohen Produktivitätsbedingungen:

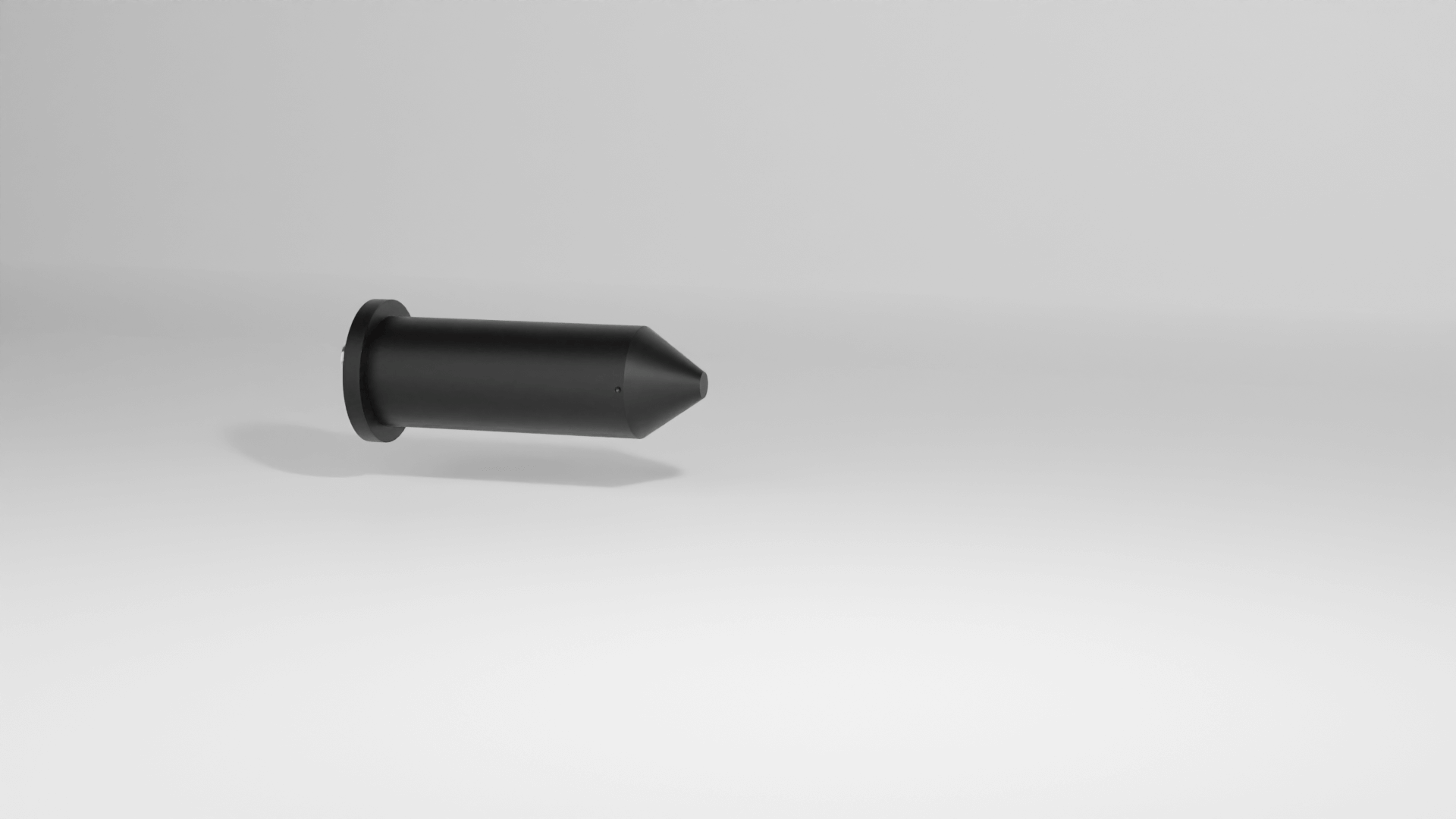

Für die Wafertypen Si, SiC, GaAs, GaN, Glas, Keramik usw. und für die Größen 1" bis 12" umfasst das gesamte Produktportfolio von SURAGUS manuelle Einzelpunktgeräte, automatisierte bildgebende Systeme und Sensor-Integrationskits für die Integration in bestehende oder neue Systeme.

Sensor XS |

Sensor S-SemiVac |

Sensor S |

Sensor M |

Für Produktanfragen kontaktieren Sie uns über